目次

unaligned data access

The Cortex-M3 supports unaligned data access.When storing 8-bit, 16-bit, or 32-bit data in a memory such as RAM, support for unaligned data access allows the data to be stored in RAM without creating wasted space.For example, SRAM memory can be reduced by more than 25%.

Benefits of Unaligned Data Access

The Cortex-M3 is a 32-bit microcontroller, so it’s aligned every 32 bits.In other words, the unit of data accessed by the CPU is 32 bits.However, when storing 8 or 16 bits of data in memory, we don’t store data across 32 bits of alignment (boundaries) unless we use unaligned data access.Therefore, 32-8 = 24 bits for 8-bit data and 32-16 = 16 bits for 16-bit data, resulting in wasted space.(See chart below, left) With unaligned data access, data is stored sequentially across 32-bit alignments (boundaries).(See right side of the figure below) This allows for efficient use of memory without wasting it.

Example of description (in the case of a tool of IAR)

To access data across alignments, define a structure with the #pragma pack(n) appended. The following is an example of a description.

#pragma pack(1)

struct {

short s; // 2 byte

char c; // 1 byte

long l; // 4 byte

char c2; // 1 byte

} s;

This fits into 8 bytes.

Is it something that is assigned differently depending on the type of compiler or the version of the compiler? The data assignments are usually the same.Please note, however, that we don’t guarantee that it will always be the same. (I can’t complain if it’s changing.)

What about the way the program is written? The way to arrange the data is defined in the manual of each compiler, so please follow the manual.(For example.Arm IAR C/C++ Development Guide)

Unaligned data access is not the first technique to be introduced in Cortex-M3. It was introduced in Armv6.

Precautions for use

While unaligned data access may seem convenient, there is one caveat.Since the Cortex-M3 is a 32-bit microcontroller, when accessing data across 32-bit alignments (boundaries), the CPU must access the data twice.This means that the efficiency of the CPU is reduced.

Be aware that using unaligned data access comes at the expense of CPU run time in exchange for RAM savings.Therefore, it is natural to think of access to data across alignments as a special kind of access via structures.The only loss in alignment is in the adjoining parts where data of different type (length) is declared, and Even if a program declares a mixture of memory lengths and types, it is collected in one place, so it is not often used except when field definitions are predetermined.

Also, it is not adopted in Cortex-M0, so you need to be careful when migrating from Cortex-M3 to Cortex-M0.

Privileges, modes and stacks

The Cortex-M3 has three key elements that are relevant to the state in which it operates. It’s a stack (stack pointer) with privileges and modes.They are all related, and Cortex-M3 works while each element is associated with the other.

privilege

A privilege is a right granted to the CPU, which is the right to access various resources of the CPU.When privileged, the CPU has access to all resources.However, in the case of unprivileged, access to some resources is limited or eliminated.

mode

The mode refers to the state in which the CPU is running.There are two modes of operation: those operated by the hardware (handler) and those operated by the user’s software.The mode operated by the hardware (handler) is called the handler mode, and the mode operated by the user’s software is called the thread mode.In handler mode, the CPU always operates with the aforementioned privileges.

stack

The stack is the place where the CPU state (context) is saved when an interrupt occurs.There is only one in a normal microcontroller, but there are two in the Cortex-M3.The use of these two stacks has to do with the aforementioned privileges and modes.

These elements are a bit more complicated, but very useful to understand. I’m going to explain this in more detail.

operating mode

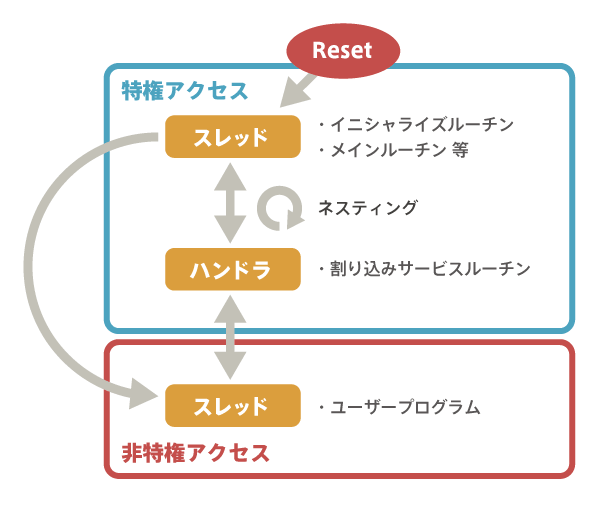

In addition to privileged and unprivileged access, the Cortex-M3 supports two modes of operation: thread mode and handler mode.It is in thread mode after a reset and so on, but enters handler mode when an exception occurs.A handler here refers to a dedicated internal program (Including the behavior of the hardware) that is invoked by exception handling such as interrupts and faults.In other words,(It may be slightly different.)You can say that thread mode is the mode that does normal processing and handler mode is the mode that does exception processing.

Thread mode

The processor will go into threaded mode after the reset. At this time, we are in a state of privileged access.The user can then (as previously mentioned) move on to unprivileged access by using the MSR instruction to clear the CONTROL[0] bit.That is, in the case of threaded mode, the user can choose whether to have privileged or unprivileged access.

After the reset, Cortex-M3 executes the program code described in main.c. Then, when an interrupt or fault exception is raised, it goes into handler mode.However, when you come back to the main.c code from the interrupt or fault service routine, you’re back in thread mode again.From this, it can be said that thread mode is, simply put, the mode to execute the program code described in main.c (including linked subroutines).

Again, in threaded mode, if it is changed from privileged access to unprivileged access, the user cannot revert to privileged.The handler changes the thread mode to a privileged one, for example, when an exception is raised. In other words, handler mode is always a privilege.

handler mode

The handler mode is entered as a result of interrupts and fault exception handling.Interrupt service routines and fault service routines are always executed in handler mode and with privileged access.The figure below shows the state transitions between privileged and unprivileged access, thread mode and handler mode.After a reset, the program will always be started in threaded mode with privileged access.If the user moves to unprivileged access, they will move to the threaded mode of unprivileged access at the bottom of the figure.

Regardless of whether you are in the thread mode of privileged or unprivileged access, when an exception is raised, you will always move to the handler mode in the middle of the figure.Handler mode is always privileged access.If more exceptions are raised in handler mode, they will be nested.When the service routine of the example processing is finished, it returns to the thread mode from where it was.

Privileged and non-privileged access

Privileged and unprivileged access is also referred to as supervisor access and user access.The state in which privileged access is available is called privileged mode, and the mode in which unprivileged access is available is called unprivileged mode.If you have used Motorola (now NXP) MC6800 series microcomputers, you may be familiar with them, but if you are new to them, it may be difficult to understand them.Privileged and unprivileged access in Cortex-M3 is the same as privileged and unprivileged access in Arm7.

This is not often seen in 8-bit and 16-bit microcomputers, but with 32-bit microcomputers, the use of the OS increases, so privileged and unprivileged access becomes very convenient.

What’s the difference between privileged access and non-privileged access is that privileged access allows you to do whatever you want, but Non-privileged access limits or eliminates access to some resources.Specifically, unprivileged access prevents the following:

- Use of some instructions such as CPS to set FAULTMASK and PRIMASK

- System Control Space (SCS) access to the majority of registers

Therefore, it is an effective function in a system where the microcontroller is divided into two parts, one for the system administrator and the other for the user.

In general, the kernel of the OS runs with privileged access and the Other tasks / threads (user programs) are classified by being executed with unprivileged access.This can help prevent programs running with unprivileged access from accidentally corrupting OS resources.It can also protect your system (OS, etc.) from viruses that are intentionally embedded by hackers, etc.

After a reset, this is privileged access, but it can be changed to unprivileged access by using the MSR instruction to clear the CONTROL[0] bit.Once privileged access has been changed to unprivileged access, users cannot revert to privileged access.Only handlers (hardware) can be changed to privileged access due to exception handling, etc.

It’s going to sound strange, but you can do anything you want with privileged access, so you don’t have to use non-privileged access.You can use it in privileged (supervisor) mode from start to finish.With Cortex-M0, cost and energy efficiency are priorities, so we don’t have this concept. The whole thing is about privileged access.

However, when using an OS, etc., to execute a system program and a user program, the For security reasons, we recommend that you use privileged and unprivileged access.

“もっと見る” カテゴリーなし

Mbed TLS overview and features

In this article, I'd like to discuss Mbed TLS, which I've touched on a few times in the past, Transport …

What is an “IoT device development platform”?

I started using Mbed because I wanted a microcontroller board that could connect natively to the Internet. At that time, …

Mbed OS overview and features

In this article, I would like to write about one of the components of Arm Mbed, and probably the most …